# An Improvement of IM and Power of High Power Amplifiers Using RC-Paralleled Circuits with Frequency Selectivity

Yukinobu Tarui, Satoshi Ogura \*, Kiyoharu Seino \*, and Yasushi Itoh

Mitsubishi Electric Corporation

Information Technology R&D Center

Ofuna 5-1-1, Kamakura, Kanagawa, 247 Japan

\* Kamakura Works

Kamimachiya 325, Kamakura, Kanagawa, 247 Japan

## Abstract

This paper describes the design method to improve IM and power of high power amplifiers by employing a RC-paralleled circuit with frequency selectivity in the design of input matching circuits. The RC-paralleled circuit decreases gain at low frequencies where the power level of inter-modulated signals becomes high, leading to a significant improvement of IM and power.

## Introduction

In the design of high power amplifiers for use in mobile and satellite communication systems, high linearity is required to reduce adjacent channel interference. The conventional linear power amplifier design have focused on improving linearity around carrier frequencies by using pre-distortion or feed-forward linearizers [1-2]. Recently some works have stated the importance to design matching circuits including bias circuits at low frequencies where the power level of inter-modulated signals becomes high [4,5]. These works, however, have addressed only the output matching conditions though the low frequency inter-modulated signals appear in both input and output matching circuits. In the case when high power amplifiers have a high gain at these low frequencies, the low frequency inter-modulated signals of the input matching circuit are amplified and provide a serious effect on IM and power.

To address this problem, a RC-paralleled circuit with frequency selectivity is employed in series with FETs' gate for decreasing gain at low frequencies where the power level of inter-modulated signals becomes high. In addition, a series

resistor is employed in the design of gate bias circuits for the same reason. With the use of the RC-paralleled circuit and a series resistor, an improvement of IM<sub>3</sub> up to 4.7 dB and output power up to 1 dB has been achieved for the C-band 10W GaAs FET amplifier.

## Low Frequency Components of Inter-Modulated Signals

It is well known that the inter-modulated signals are  $nf_1 + mf_2$  in two-tone excitation ( $f_1 < f_2$ , n and m are integer). Among these inter-modulated signals, the low frequency components are n times of separation frequency, that is,  $f_2 - f_1$ ,  $2(f_2 - f_1)$ ,  $3(f_2 - f_1)$ , ... . The frequency separation of two tones is  $f_2 - f_1$ , which is expressed as  $\Delta f$ . In the case when terminations of high power amplifier becomes short at low frequency, the voltage of the low frequency inter-modulated signals becomes zero, not degrading IM and power characteristics. In the actual case, however, it becomes difficult to make the impedances of matching circuits ideally short at these low frequencies. Therefore, the low frequency inter-modulated signals vary the gate and drain bias conditions and degrade IM and power performance.

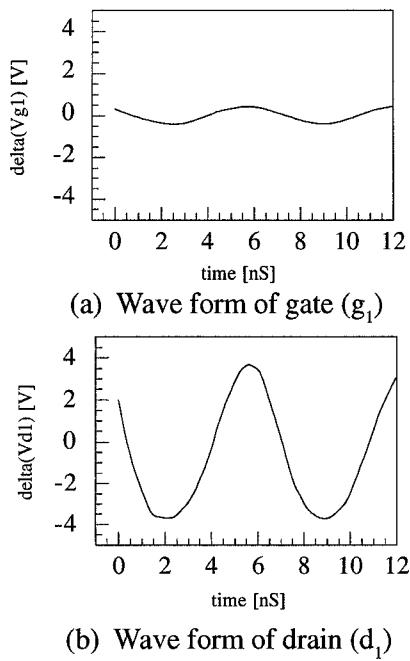

As an example, time-domain waveforms of the gate and drain voltages of the 7-GHz 10 W GaAs FET amplifier were measured below 1 GHz at nodes  $g_1, d_1$ , respectively and is shown in Fig. 1, where  $\Delta f$  is 150 MHz and the impedance of the input and output matching circuits is not ideally short below 1 GHz. The variation of the gate voltage is  $-2.5 \pm 0.4$  V and that of the drain voltage is  $9 \pm 3.7$  V. It is clearly shown that the lowest inter-modulated signal ( $\Delta f$ ) appears in both input and output matching circuits, which is considered to have a serious effect on IM and power performance.

Fig. 1 Time-domain waveforms of the gate and drain voltages of the 7-GHz 10W GaAs FET amplifier.

### Design of RC-Paralleled Circuits

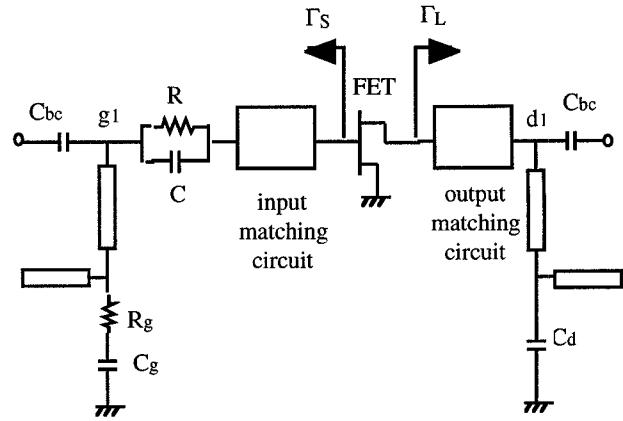

A schematic diagram of the 7-GHz 10W GaAs FET amplifier with a RC-paralleled circuit is shown in Fig. 2. The amplifier is comprised of four of the 18.9 mm GaAs MESFETs, input and output matching circuits, gate and drain bias circuits, and a RC-paralleled circuit. To improve IM and power of the amplifier, the impedance of input and output matching circuits has to be short at  $\Delta f$ ,  $2\Delta f$ ,  $3\Delta f$ , ... . That is, the values of the bypass capacitors ( $C_g$  and  $C_d$ ) have to be designed as large as possible. Then the value of the series resistor ( $R_g$ ) of the gate bias circuit is designed to minimize gain at  $\Delta f$ ,  $2\Delta f$ ,  $3\Delta f$ , ... . Finally, a RC-paralleled circuit is connected in series with FETs' gate to selectively decrease gain at  $\Delta f$ ,  $2\Delta f$ ,  $3\Delta f$ , ... . The condition that the RC-paralleled circuit becomes resistive at a low frequency ( $f_L$ ) and capacitive at a high frequency ( $f_H$ ) is as follows:

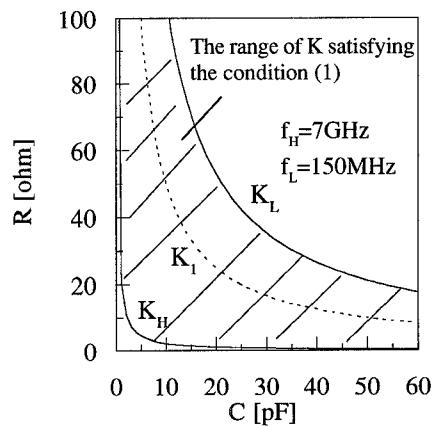

$$\frac{1}{2\pi f_H} (= K_H) < K < \frac{1}{2\pi f_L} (= K_L) \quad (1)$$

where  $K = RC$ . In the case of the 7-GHz 10 W GaAs FET amplifier with  $\Delta f = 150$  MHz,  $f_L$  is 150 MHz and  $f_H$  is 7

Fig. 2 Schematic diagram of the 7-GHz 10W GaAs FET amplifier with a RC-paralleled Circuit.

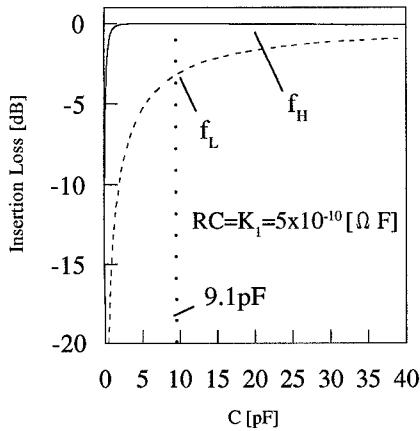

GHz. The range of  $K$  satisfying the condition (1) with a parameter of  $R$  and  $C$  is shown in Fig. 3. In addition, the insertion loss of the RC-paralleled circuit is calculated for a constant value of  $K$  and is shown in Fig. 4. It is noted in Fig. 4 that a low value of  $C$  and a high value of  $R$  are desirable to maximize the insertion loss at  $f_L$  and minimize the insertion loss at  $f_H$ . However, a high value of  $R$  causes a gate bias variation due to a gate current ( $I_{gs}$ ) under large-signal operation. Therefore, the values of  $R$  and  $C$  were obtained to keep  $|(R+R_g)I_{gs}| < 0.1$  V in addition to maximizing the insertion loss at  $f_L$  and minimizing the insertion loss at  $f_H$  within the range of  $K$  shown in Fig. 2. The final values of  $R$  and  $C$  were  $R = 50\Omega$  and  $C = 9.1$  pF. The gain

Fig. 3 Range of  $K$  satisfying the condition (1) with a parameter of  $R$  and  $C$ .

Fig. 4 Insertion loss of the RC-paralleled circuit.

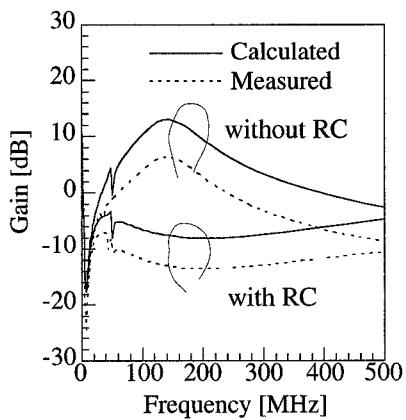

of the 7-GHz 10W GaAs FET amplifier with and without using the RC-paralleled circuit are calculated for the schematic diagram shown in Fig. 1. The calculated results are shown in Fig. 5. The small-signal model parameters of the 18.9 mm GaAs MESFET are summarized in Table 1. The values of  $C_g$  and  $C_d$  were determined to  $0.1\mu\text{F}$ . The value of  $R_g$  was determined to  $5\Omega$ . The measured results are also shown in Fig. 5. It is clearly shown that the gain can be reduced to 20 dB for  $\Delta f = 120$  to  $150$  MHz with the use of the RC-paralleled circuit.

Fig. 5 Gain of the 7-GHz 10W GaAs FET amplifier at low frequency with and without using the RC-paralleled circuit.

RC-paralleled circuit :  $R=50\Omega$ ,  $C=9.1\text{pF}$

$C_g=C_d=0.1\mu\text{F}$ ,  $R_g=5\Omega$

Table 1 Small-signal model parameters of the 18.9 mm GaAs MESFET.

| Wg             | 18.9mm |

|----------------|--------|

| $L_g$ (nH)     | 0.016  |

| $L_d$ (nH)     | 0.026  |

| $L_s$ (nH)     | 0.001  |

| $C_{gs}$ (pF)  | 16.8   |

| $C_{dg}$ (pF)  | 0.78   |

| $C_{ds}$ (pF)  | 3.1    |

| $C_{gds}$ (pF) | 0.025  |

| $C_{dss}$ (pF) | 0.015  |

| $R_g$ (ohm)    | 0.3    |

| $R_i$ (ohm)    | 0.31   |

| $R_s$ (ohm)    | 0.02   |

| $R_d$ (ohm)    | 0.4    |

| $R_{ds}$ (ohm) | 10.4   |

### Improvement of IM and Power

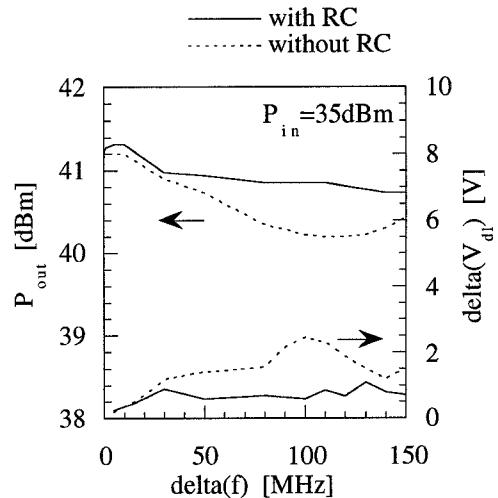

The measured output power ( $P_{out}$ ) and variations of the gate and drain voltages ( $V_g$  and  $V_d$ ) of the 7-GHz 10W GaAs FET amplifier with and without using the RC-paralleled circuit are shown in Fig. 6, where  $\Delta f$  is varied from 0 to 150 MHz. The output power was improved up to 0.6 dB by using the RC-paralleled circuit for an input power of 35 dBm. The variation of  $V_d$  ( $\Delta V_d$ ) were also improved up to 2.0V. For  $\Delta f = 120$  to  $130$  MHz, the output power was greatly improved, which corresponds to the gain reduction

Fig. 6 Output power and variations of the gate and drain voltages of the 7-GHz 10W GaAs FET amplifier with and without using the RC-paralleled circuit.

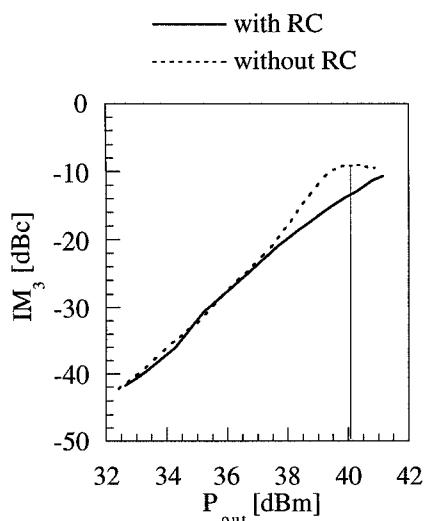

Fig. 7 Measured  $IM_3$  vs  $P_{out}$  at  $\Delta f = 120$  MHz.

shown in Fig. 5. The measured  $IM_3$  vs  $P_{out}$  at  $\Delta f = 120$  MHz is plotted in Fig. 7. The improvement of  $IM_3$  with the RC-paralleled circuit was 4.7 dB at  $P_{out} = 40$  dBm.

### Conclusion

We have presented the design method to improve IM and power of high power amplifiers by employing the RC-paralleled circuit with frequency selectivity in the design of input matching circuits. It has been clearly shown in experiment that the RC-paralleled circuit selectively decreases gain at low frequencies where the power level of inter-modulated signals becomes high and improves the variation of the gate and drain voltages, leading to the significant improvement of IM and power performance.

### References

- [1] M. Nakayama, K. Mori, K. Yamauchi, Y. Itoh, and Y. Mitsui, "A Novel Amplitude and Phase Linearizing Technique for Linear Power Amplifiers," *Microwave Journal*, vol. 39, No. 3, pp. 96-104, March 1996.

- [2] T. Nojima and S. Narahashi, "Extremely Low-Distortion Multi-Carrier Amplifier for Mobile Communication Systems - Self-Adjusting Feed-Forward Amplifier," *IEICE Technical Report*, RCS90-4, 1990.

- [3] H. Kawasaki, T. Ohgihara, and Y. Murakami, "An Investigation of  $IM_3$  Distortion in Relation to Bypass Capacitor of GaAs MMIC's," *1996 IEEE MMWMC-S Digest*, pp. 119-122.

- [4] N. Matsuno, H. Yano, Y. Suzuki, and K. Honjo, "Intermodulation Distortion Dependence on Bias Circuit Design in Power MOSFETs," *IEICE NTCV*, C-2-23, March 1997.